# M61040FP

## Smart Battery Protection and Monitoring IC

REJ03F0237-0200 Rev.2.00 Mar 18, 2008

### Description

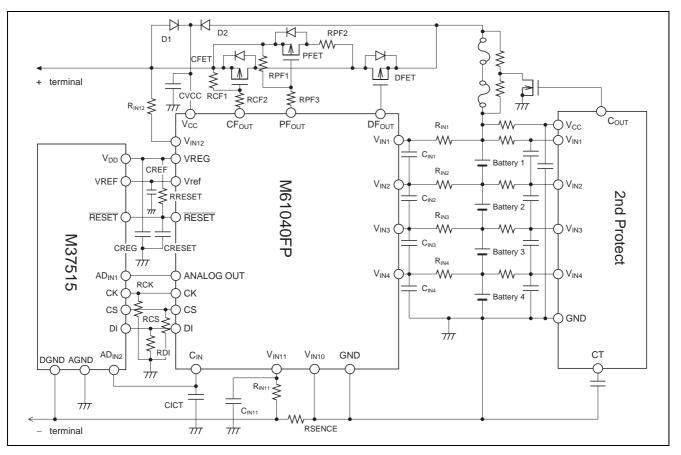

The M61040FP is intended to be used as SB: Smart Battery.

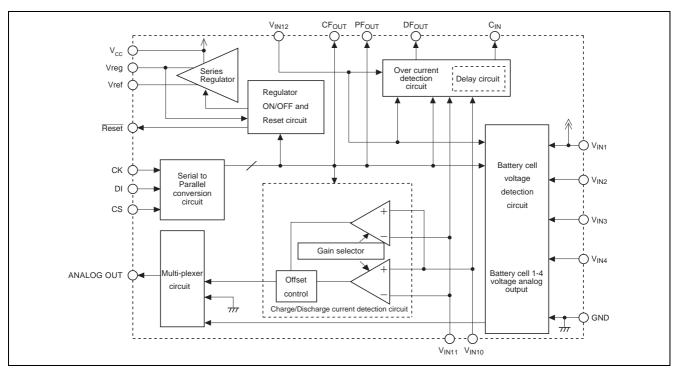

All functions needed for SB are packed to this M61040FP. The combination use with microcomputer such as M37515 will give various functions such as a detection or calculation of SB remaining capacity. Over current detection circuit dedicated in M61040FP will give safety FET on/off control independent from microcomputer control.

The amp gain of charge/discharge current detection circuit is controlled by microcomputer, therefore the accuracy of SB's remaining capacity detection becomes better than before. The reset circuit and the linear regulator for  $V_{CC}$ /Vref of microcomputer are dedicated in M61040FP. So this will help easy design of power circuit design of SB.

## Features

- Built-in high gain op-amps for monitoring charge/discharge current

- Built-in over current detection circuit for FET protection

- All FETs are controlled by microcomputer

- Various powers saving function to reduce total power dissipation

- High input voltage device (absolute maximum rating: 33 V)

## Application

Smart battery system

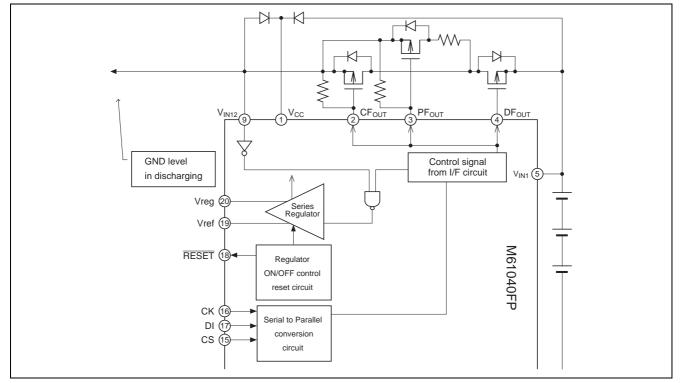

## Block Diagram

RENESAS

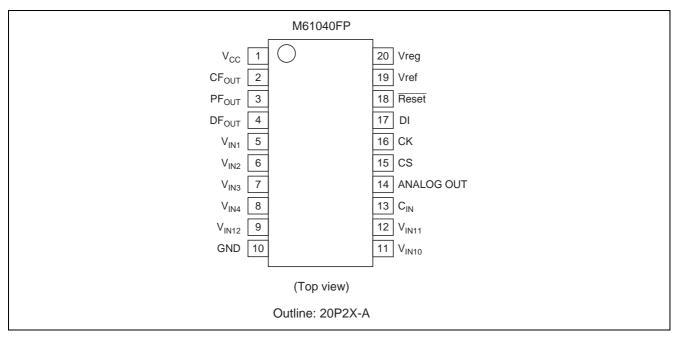

## **Pin Arrangement**

## **Pin Description**

| Pin No. | Pin Name          | Functions                                                                                          |

|---------|-------------------|----------------------------------------------------------------------------------------------------|

| 5       | V <sub>IN1</sub>  | Battery 1 + voltage input                                                                          |

| 6       | V <sub>IN2</sub>  | Battery 1 – voltage and battery 2 + voltage input                                                  |

| 7       | V <sub>IN3</sub>  | Battery 2 – voltage and battery 3 + voltage input                                                  |

| 8       | V <sub>IN4</sub>  | Battery 3 – voltage and battery 4 + voltage input                                                  |

| 9       | V <sub>IN12</sub> | Monitoring charger is connected or not                                                             |

| 13      | C <sub>IN</sub>   | Connect capacitor for over current detection delay                                                 |

| 11      | V <sub>IN10</sub> | Charge/discharge current monitor input and connects charge/discharge current sense resistor        |

| 12      | V <sub>IN11</sub> | Charge/discharge current monitor input and connects charge/discharge current sense resistor        |

| 1       | V <sub>CC</sub>   | Power source pin. Power from charger or battery                                                    |

| 10      | GND               | Ground                                                                                             |

| 20      | Vreg              | Linear-regulator output for microcomputer                                                          |

| 19      | Vref              | Vreg voltage output for Vreg of microcomputer, Max 200 $\mu$ A/5 V                                 |

| 18      | RESET             | Reset signal output to RESET of microcomputer                                                      |

| 14      | ANALOG OUT        | Various analog signal outputs to AD-input of microcomputer                                         |

| 4       | DF <sub>OUT</sub> | Discharge FET-drive output. The driver is turned off when over current detected.                   |

| 2       | CF <sub>OUT</sub> | Charge FET-drive output. The driver is turned off by microcomputer.                                |

| 17      | DI                | Input of 6-bit length serial data from microcomputer                                               |

| 16      | СК                | Input of shift clock from microcomputer. DI's input data is latched by low-to-high edge of this CK |

| 15      | CS                | During low signal input to this CS, data input to DI is enabled.                                   |

| 3       | PF <sub>OUT</sub> | Pre-charge FET-drive output. The driver is turned off by microcomputer.                            |

## Absolute Maximum Ratings

| ltem                        | Symbol          | Ratings     | Unit |

|-----------------------------|-----------------|-------------|------|

| Absolute maximum rating     | Vabs            | 33          | V    |

| Supply voltage              | V <sub>CC</sub> | 30          | V    |

| Power dissipation           | Pd              | 750         | mW   |

| Operating temperature range | Topr1           | -20 to +85  | °C   |

| Storage temperature range   | Tstg            | -40 to +125 | °C   |

## **Electrical Characteristics**

|                 |                                        |                   |                                   |                 | (1a = 25)                         | °C, V <sub>C</sub> | $_{\rm C} = 14$ V | , unless otherwise noted)     |

|-----------------|----------------------------------------|-------------------|-----------------------------------|-----------------|-----------------------------------|--------------------|-------------------|-------------------------------|

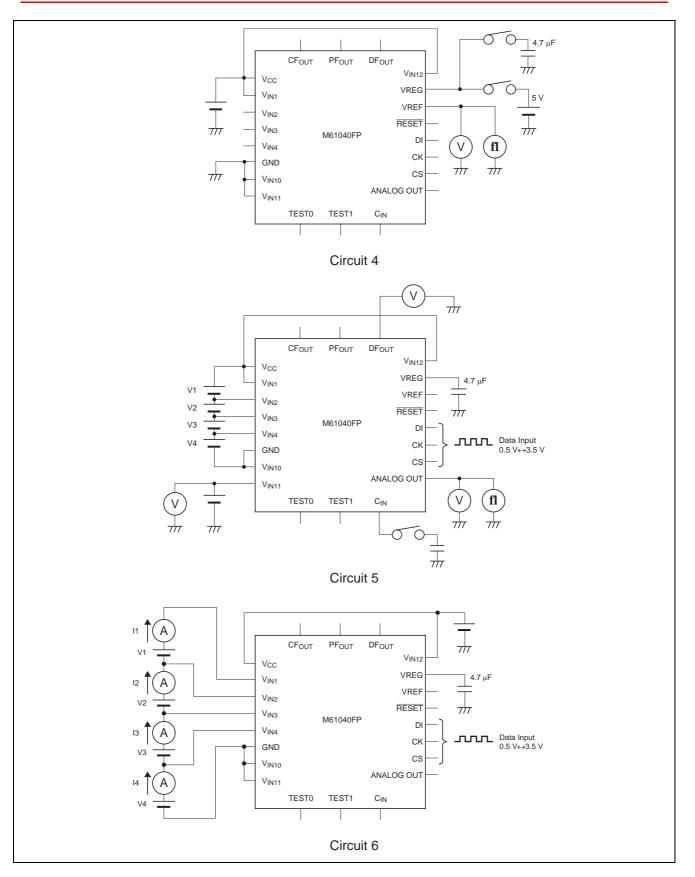

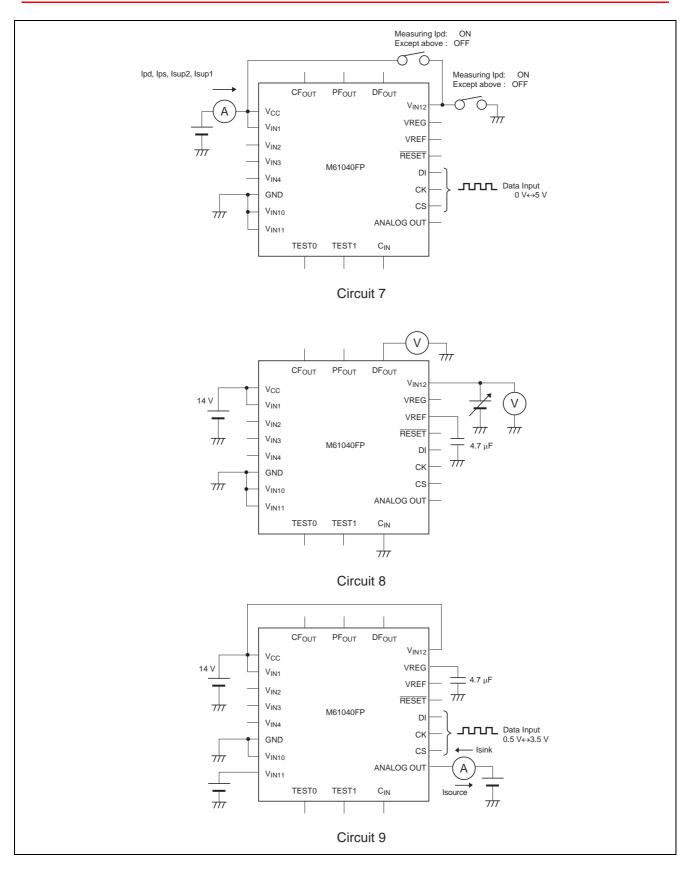

|                 | Item                                   | Symbol            | Min                               | Тур             | Max                               | Unit               | Circuit           | Test Conditions               |

| Total           | Supply voltage                         | V <sub>cc</sub>   | _                                 | _               | 30                                | V                  |                   |                               |

|                 | Supply current 1                       | lsup1             | 105                               | 200             | 280                               | μΑ                 | 7                 | Voltage monitor, V/R,         |

|                 |                                        |                   |                                   |                 |                                   |                    |                   | reset ON, current monitor ON  |

|                 | Supply current 2                       | lsup2             | 65                                | 120             | 165                               | μΑ                 | 7                 | Voltage monitor, V/R,         |

|                 |                                        |                   |                                   |                 |                                   |                    |                   | reset ON, current monitor OFF |

|                 | Supply current                         | lps               | 35                                | 60              | 85                                | μA                 | 7                 | Regulator ON, non-loading,    |

|                 | (at power save mode)                   |                   |                                   |                 |                                   |                    |                   | reset circuit ON, others OFF  |

|                 | Supply current                         | lpd               | —                                 | —               | 0.5                               | μA                 | 7                 | All operation stop,           |

|                 | (at power down                         |                   |                                   |                 |                                   |                    |                   | $V_{IN}12 = GND$              |

| Desudates       | mode)                                  | ) (no n           | E 4 4 E                           | 5.0             | 5 005                             | V                  |                   |                               |

| Regulator       | Output voltage                         | Vreg              | 5.145                             | 5.2             | 5.295                             | V                  | 3                 | lout = 20 mA                  |

|                 | Input and output<br>voltage difference | Vdif0             | —                                 | 0.3             | 0.8                               | V                  | 3                 | lout = 20 mA                  |

|                 | Linear regulation                      | $\Delta$ Vout10   | —                                 | 100             | 200                               | mV                 | 3                 | $V_{CC} = 6.2$ to 24 V,       |

|                 |                                        |                   |                                   |                 |                                   |                    |                   | lout = 20 mA                  |

|                 | Load regulation                        | $\Delta$ Vout20   | —                                 | 30              | 45                                | mV                 | 3                 | V <sub>CC</sub> = 6.2 V,      |

|                 |                                        |                   |                                   |                 |                                   |                    |                   | lout = 50 μA to 20 mA         |

|                 | Input voltage                          | V <sub>IN</sub> 0 | —                                 | —               | 30                                | V                  |                   | V <sub>CC</sub> voltage       |

| Reference       | Output voltage                         | Vref              | 4.818                             | 4.85            | 4.917                             | V                  | 4                 | lout = 200 μA                 |

| voltage         | Load stability                         | $\Delta$ Vout21   | —                                 | 5               | 45                                | mV                 | 4                 | V <sub>CC</sub> = 6.2 V,      |

|                 |                                        |                   |                                   |                 |                                   |                    |                   | lout = 50 to 200 μA           |

| Over current    | Over current inhibit                   | Vcl               | VCL - 0.02                        | 0.2             | VCL + 0.02                        | V                  | 8                 |                               |

| detection       | detection voltage 1                    |                   |                                   |                 |                                   |                    |                   |                               |

|                 | Over current inhibit                   | Vch               | $\frac{\text{Vcc}}{3} \times 0.6$ | $\frac{Vcc}{3}$ | $\frac{\text{Vcc}}{3} \times 1.4$ | V                  | 8                 | Load short detection          |

|                 | detection voltage 2                    |                   | <u> </u>                          |                 | <u> </u>                          |                    |                   |                               |

|                 | Over current inhibit                   | Tvcl              | 7                                 | 10              | 15                                | ms                 | 5                 | CICT = 0.01 μF                |

|                 | detection delay time 1                 |                   |                                   |                 |                                   |                    |                   |                               |

|                 | Over current inhibit                   | Tvch              | 150                               | 250             | 350                               | μS                 | 8                 |                               |

| -               | detection delay time 2                 |                   |                                   |                 |                                   |                    |                   |                               |

| Battery voltage | Input offset voltage                   | Voff1             | 31                                | 208             | 385                               | mV                 | 5                 |                               |

| detection       | Voltage gain 1                         | Gamp1             | 0.99                              | 1.0             | 1.01                              |                    | 5                 |                               |

|                 | Output source current                  | Isource1          | 150                               |                 | —                                 | μΑ                 | 10                |                               |

|                 | Output sink current                    | lsink1            | 150                               | —               | —                                 | μΑ                 | 10                |                               |

|                 | Detection voltage of                   | Vref-Voff1        | 4.45                              | —               | —                                 | V                  | 5, 6              |                               |

|                 | battery cell                           |                   |                                   |                 |                                   |                    |                   |                               |

$(Ta = 25^{\circ}C, V_{CC} = 14 V, unless otherwise noted)$

|              | Item                      | Symbol            | Min   | Тур  | Max   | Unit | Circuit | Test Conditions     |

|--------------|---------------------------|-------------------|-------|------|-------|------|---------|---------------------|

| Charge/      | Input offset voltage      | Voff2             | 0.2   | 2    | 3.8   | V    | 5       | Gain = 200 selected |

| discharge    | Voltage gain 21           | Gain21            | 38.4  | 40   | 41.6  | V    | 5       |                     |

| current      | Voltage gain 22           | Gain22            | 96    | 100  | 104   | V    | 5       |                     |

| detection    | Voltage gain 23           | Gain23            | 192   | 200  | 208   | V    | 5       |                     |

|              | Output source current     | Isource2          | 150   | _    | _     | μA   | 9       |                     |

|              | Output sink current       | lsink2            | 150   | _    | _     | μA   | 9       |                     |

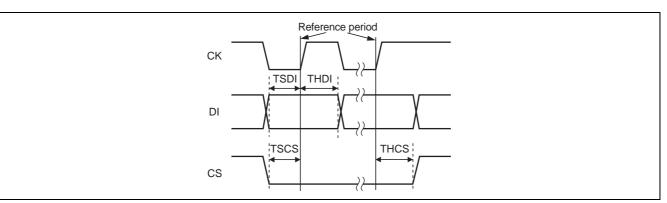

| Interface    | DI input H voltage        | VDIH              | 3.5   | _    | Vreg  | V    | 1       |                     |

|              | DI input L voltage        | VDIL              | 0     | _    | 0.5   | V    | 1       |                     |

|              | CS input H voltage        | VCSH              | 3.5   | _    | Vreg  | V    | 1       |                     |

|              | CS input L voltage        | VCSL              | 0     | _    | 0.5   | V    | 1       |                     |

|              | CK input H voltage        | VCKH              | 3.5   | _    | Vreg  | V    | 1       |                     |

|              | CK input L voltage        | VCKL              | 0     | _    | 0.5   | V    | 1       |                     |

| Reset        | Detection voltage1        | Vdet-             | 3.045 | 3.25 | 3.475 | V    | 2       |                     |

|              | Release voltage1          | Vdet+             | 4.16  | 4.2  | 4.27  | V    | 2       |                     |

| Conditioning | V <sub>IN1</sub> resistor | R <sub>INV1</sub> | 4.4   | 12   | 27    | kΩ   | 6       |                     |

| circuit      | V <sub>IN2</sub> resistor | R <sub>INV2</sub> | 4.4   | 12   | 27    | kΩ   | 6       |                     |

|              | V <sub>IN3</sub> resistor | R <sub>INV3</sub> | 4.4   | 12   | 27    | kΩ   | 6       |                     |

|              | V <sub>IN4</sub> resistor | R <sub>INV4</sub> | 4.4   | 12   | 27    | kΩ   | 6       |                     |

## **Operation Description**

M61040 is developed for intelligent Li-ion battery pack such as SB in SBS. M61040 is suitable for smart battery.

- SBS: Smart Battery System introduced by Intel and Duracell

- SB: Smart Battery which contains 3 or 4 series Li-ion battery cells.

All analog circuits are included to M61040. Therefore pair using with microcomputer such as M37515 and small additional parts will give various functions such as battery remaining capacity detection. All functions are described as follows:

- Voltage detection circuit of each Li-ion battery cells M61040 can output each battery cell's voltage of 3 or 4 series connection. Built-in buffer amplifier is monitoring each battery voltage. Microcomputer can adjust the offset voltage.

- 2. Charge/discharge current detection circuit

In SBS, remaining capacity check function (Gas-gage function) is necessary. To calculate accurate remaining capacity, microcomputer must get charge/discharge current periodically. Accurate charge/discharge current of external sense register is monitored by built-in amp. The charge/discharge current is converted to voltage value through the accurate sense resistor.

Output gain can be controlled by microcomputer. Off-set voltage can be set lower by external parts, therefore dynamic range of microcomputer's A to D converter will widen.

3. Over current detection circuit

M61040 contains over current detection circuit. The discharging FET is turned off to stop discharging and it continues for the over current detection delay time (tIOV1) or longer, if the discharging current becomes equal to or higher than a specified value. It is necessary for safety of Li-ion battery pack. Delay time is set by external capacity connected to CIN. Also the voltage of CIN shows detection or NOT detection of over current. Over current detection is controlled independently by this M61040's built-in hardware NOT by microcomputer's software control.

4. Series regulator, reference voltage

M61040 contains low drop out series regulator. Microcomputer in SB does not need any additional voltage regulator, Max 20 mA/5 V. Also M61040 gives very accurate reference voltage as 4.85 V for Vref voltage for microcomputer's A to D converter.

5. Reset circuit for microcomputer

Vreg output voltage is checked by reset circuit of M61040. Therefore, lower voltage of Vreg issues RESET signal to stop mull-function of microcomputer. Also, lower voltage after long time's left issues RESET signal to stop mull-function of microcomputer. This function is useful for safety of long time's left battery.

When charger is connected to SB, this circuit will check Vreg voltage, so if Vreg voltage is NOT enough high, this circuit remains low as for RESET signal to microcomputer.

6. Power save function

M61040FP contains power save function to control several supply current.

The function and control method are shown as table 1.

The function of battery voltage detection circuit, charge/discharge detection circuit, over current detection circuit can be stopped as the need arises.

#### Table 1

| Control Method       | Battery Voltage<br>Detection Circuit    | Charge/Discharge<br>Detection Circuit | Over Current<br>Detection Circuit |  |  |

|----------------------|-----------------------------------------|---------------------------------------|-----------------------------------|--|--|

| Software control     | 0                                       | 0                                     | 0                                 |  |  |

| (through serial I/F) | Each function can be ON/OFF separately. |                                       |                                   |  |  |

— Enter power down mode

Microcomputer issues shot-down command to M61040 after microcomputer detects that battery voltage is too low. After this command, the DFOUT pin is set to "high" and the  $V_{IN12}$  pin is pulled down by internal resistor to be set "low" and series regulator are turned off.

In the power down mode, the M61040 operation is impossible. And CFOUT, DFOUT and PFOUT pins are set to "high". (In this situation, both charging and discharging are forbidden.)

At this time, supply current becomes Max 1.0 µA, so drops of battery voltage is prevented.

Figure 2 Function after Detecting Over-discharge

- Resume from power down mode

After entering power down mode, the series regulator will begin operation when charger is connected ( $V_{IN12}$  pin is high). The RESET will output low to high signal when Vreg is over reset level voltage. Microcomputer will begin operation and send command to resume M61040 from power down mode.

7. Conditioning circuit

M61040 have a discharge circuit of each cells. It is available for drop of cell voltage for safety purpose. And to shorten the difference voltage among the cells. It can extend the battery pack life.

## **Measurement Circuit**

## **Block Diagram Description**

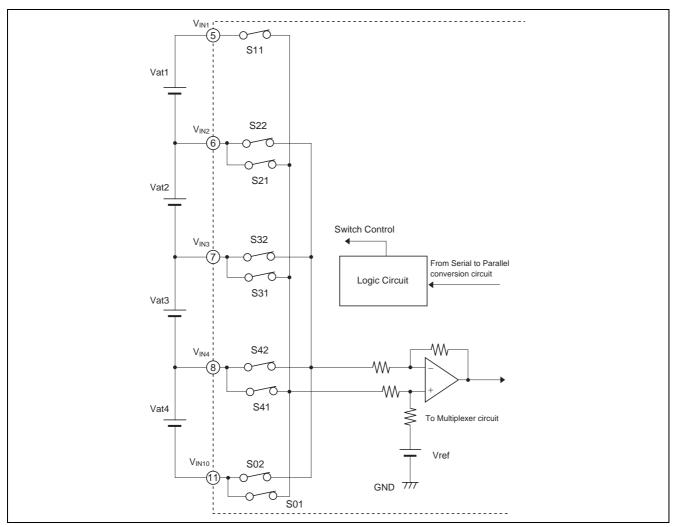

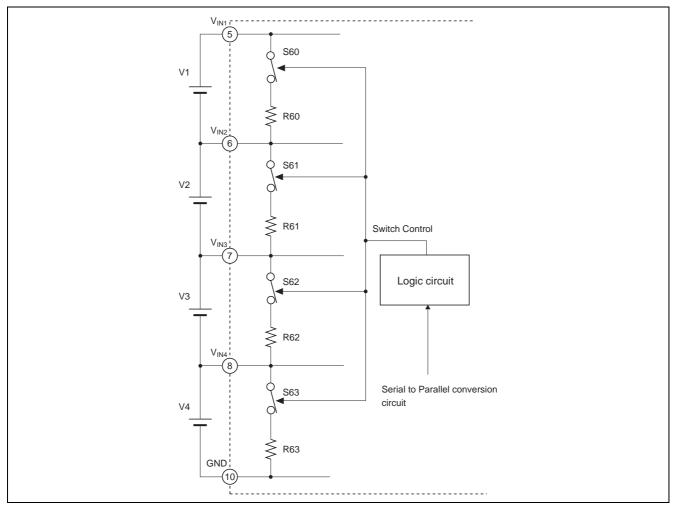

(1) Battery voltage detection circuit

The M61040 battery voltage detection circuit is shown in figure 3.

This circuit is composed of switch, buffer amplifier, reference voltage section and logic circuit.

Microcomputer selects detecting voltage before logic circuit controls the connection of switches. This connection decides which cell voltage (Vbat1, Vbat2, Vbat3, Vbat4) should be output from analog out pin. Besides offset voltage can be output.

In power down mode, supply current in this block is close to zero because all switches are off.

Note: Regard 50 µs as the standard of settling time by voltage change in this block.

Figure 3 Battery Voltage Detection Circuit

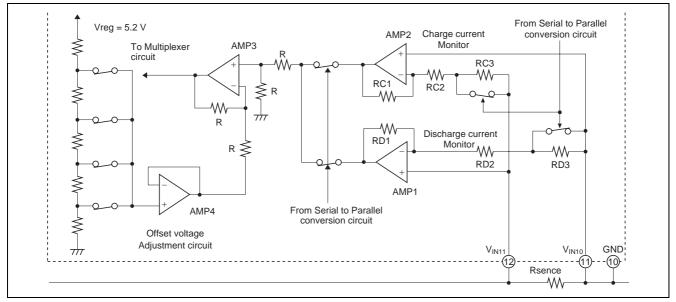

(2) Charge/discharge current detection circuit

The charge/discharge current detection circuit is shown in figure 4. This circuit is composed of offset voltage adjustment circuit, buffer amplifier and resistor network.

The pre-amplifier amplifies the voltage of sense resistance to the voltage based on GND. The voltage gain can be selected by microcomputer commands.

Buffer amplifier does an impedance translation between input and output.

Figure 4 Charge/Discharge Current Detection Circuit

The offset voltage can be compensated by adjustment circuit.

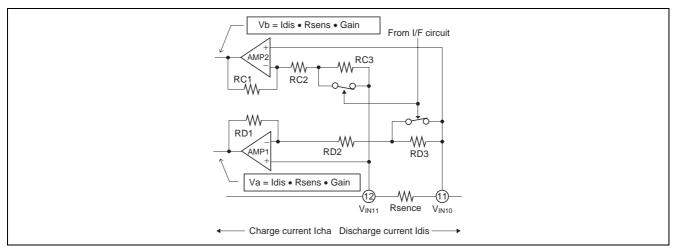

The function in detecting discharge current is shown in figure 5. The differential voltage of sense resistor is input to + (plus) terminal of AMP 1 when discharge current is flowing in sense resistor. Selecting high voltage gain by microcomputer's command is capable of monitoring very little discharge current accurately.

The differential voltage of sense resistor is input to - (minus) terminal of AMP 2 when charge current is flowing in sense resistor. The methods of detecting in charging are the same as in discharging except that AMP2 reverses input voltage before outputting.

Note: Regard 500 µs as the standard of settling time by voltage change in this block.

Figure 5 Charge/Discharge Current Detection

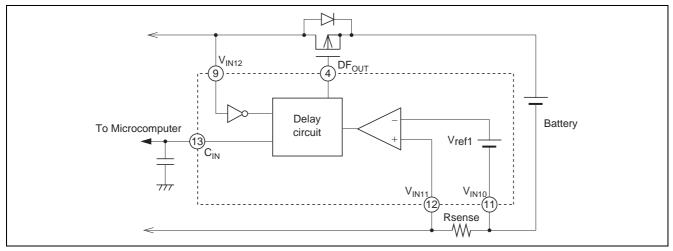

#### (3) Over current detection circuit

The over current detection circuit is shown in figure 6. This circuit is composed of comparator, reference voltage and delay circuit.

It can be got high accuracy over current detection by adjusting detection voltage with sense resistor. Microcomputer can detect the over current status through monitoring " $C_{IN}$ " pin.

Besides this block contains load-short detection circuit. This circuit detects load-short with  $V_{IN12}$  pin and protects faster than over current detection.

Figure 6 Over Current Detection Circuit

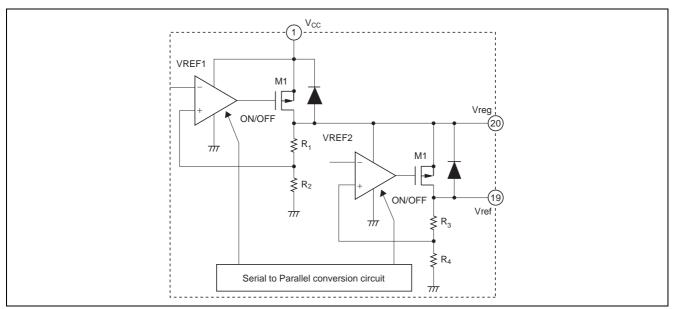

(4) Voltage regulator and reference voltage

Voltage regulator and reference circuit are shown in figure 7. Pch MOS transistor is used for output driver. The output voltage can be adjusted by M61040 itself. So the external resistor is not required.

Note: There is a diode put between  $V_{CC}$  and Vreg terminal to prevent the invert current from damaging this IC when  $V_{CC}$  voltage is higher than Vreg voltage. So please always keep Vreg voltage lower than  $V_{CC} + 0.3$  V. Set a condenser on output to suppress input changes or load changes.

Figure 7 Voltage Regulator Circuit

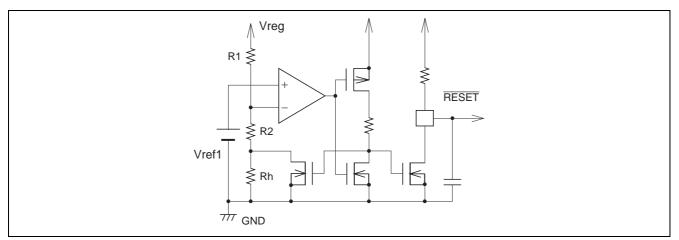

(5) Reset circuit

The M61040 reset circuit is shown in figure 8. This circuit is composed of comparator, reference voltage section and breeder resistor.

The reset output is Nch open drain structure so the reset delay time depends on external CR value.

The reset circuit monitors Vreg output to prevent microcomputer abnormal operation when  $V_{CC}$  voltage goes down abnormally.

Figure 8 Reset Circuit

#### (6) Conditioning circuit

The M61040 conditioning circuit is shown in figure 9. This circuit is composed of switch, resistor and logic circuit. According to the serial data from microcomputer, the logic circuit can individually control the switches (S60, S61 ... etc.) to do individual cell discharge to a select voltage.

This circuit is capable of making all sells discharge at the same time.

Figure 9 Conditioning Circuit

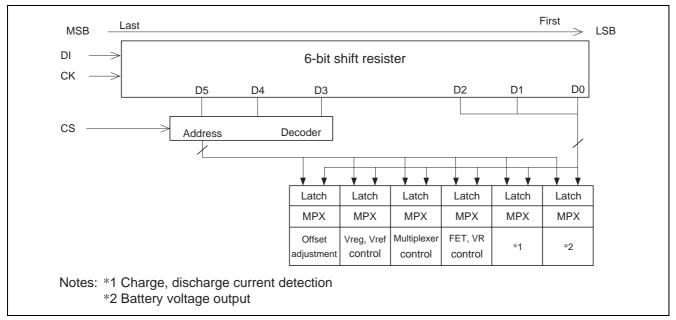

## **Digital Data Format**

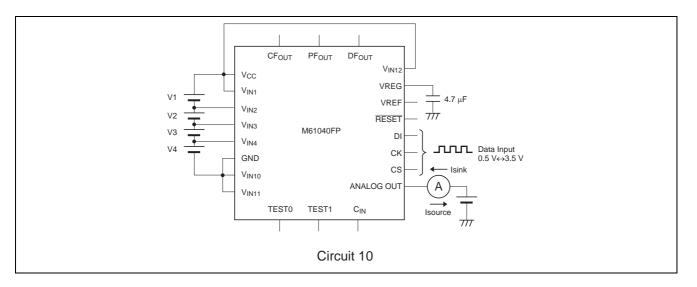

Figure 10 Serial to Parallel Conversion Circuit

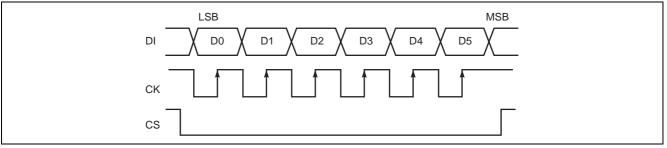

## **Data Timing Example**

Figure 11 Serial to Parallel Timing Chart

## **Data Timing**

### Table 2

|                                    |    | Address |    |    | Data |    |                  |

|------------------------------------|----|---------|----|----|------|----|------------------|

| Establishment Data                 | D5 | D4      | D3 | D2 | D1   | D0 | Contents         |

| Reset                              | 0  | 0       | 0  | —  | _    | —  |                  |

| Battery voltage output             | 0  | 0       | 1  | —  | _    | —  | Refer to table 3 |

| Offset adjustment                  | 0  | 1       | 0  | —  |      | —  | Refer to table 4 |

| Charge/discharge current detection | 0  | 1       | 1  | —  |      | —  | Refer to table 5 |

| FET control                        | 1  | 0       | 0  | —  |      | —  | Refer to table 6 |

| Multiplexer select                 | 1  | 0       | 1  | _  |      | —  | Refer to table 7 |

| Conditioning circuit               | 1  | 1       | 0  | _  |      | —  | Refer to table 8 |

| Regulator over current control     | 1  | 1       | 1  | —  |      | —  | Refer to table 9 |

### Table 3 Battery Voltage Output

| D2 | D1 | D0 | Output Voltage               | Detail                |

|----|----|----|------------------------------|-----------------------|

| 0  | 0  | 0  | V1                           |                       |

| 0  | 0  | 1  | V2                           |                       |

| 0  | 1  | 0  | V3                           |                       |

| 0  | 1  | 1  | V4                           |                       |

| 1  | 0  | 0  | Connect to V <sub>IN2</sub>  | Offset voltage output |

| 1  | 0  | 1  | Connect to V <sub>IN3</sub>  | Offset voltage output |

| 1  | 1  | 0  | Connect to V <sub>IN4</sub>  | Offset voltage output |

| 1  | 1  | 1  | Connect to V <sub>IN10</sub> | Offset voltage output |

Note: V1 battery voltage output when system reset

#### Table 4 Offset Voltage Control Section of Discharge Current Monitor Amplifier

|    |    |    | Output               |

|----|----|----|----------------------|

| D2 | D1 | D0 | Offset Voltage Value |

| 0  | 0  | 0  | No offset (0 V)      |

| 0  | 0  | 1  | 1 V                  |

| 0  | 1  | 0  | 2.1 V                |

| 0  | 1  | 1  | 3.1 V                |

| 1  | 0  | 0  | 3.7 V                |

| 1  | 0  | 1  | 1 V                  |

| 1  | 1  | 0  | 1 V                  |

| 1  | 1  | 1  | 1 V                  |

Note: No offset voltage when system reset

### Table 5 Charge and Discharge Current Detection

| D2 | D1 | D0 | Mode                    | Output                           |

|----|----|----|-------------------------|----------------------------------|

| 0  | 0  | 0  | AMP stop, resistor open | AMP operation stop, current save |

| 0  | 0  | 1  | Gain × 40 output        |                                  |

| 0  | 1  | 0  | Gain × 100 output       |                                  |

| 0  | 1  | 1  | Gain × 200 output       |                                  |

| 1  | 0  | 0  | AMP stop, resistor open | AMP operation stop, current save |

| 1  | 0  | 1  | Offset output (× 40)    |                                  |

| 1  | 1  | 0  | Offset output (× 100)   |                                  |

| 1  | 1  | 1  | Offset output (× 200)   |                                  |

Note: Amplifier operation is stopped when system reset

#### Table 6 FET Regulator Control

|    |    |    | FET Connection Terminal    |                            |                            |  |

|----|----|----|----------------------------|----------------------------|----------------------------|--|

| D2 | D1 | D0 | CF <sub>OUT</sub> Terminal | DF <sub>OUT</sub> Terminal | PF <sub>OUT</sub> Terminal |  |

| 0  | 0  | 0  | High                       | High                       | High                       |  |

| 0  | 0  | 1  | High                       | High                       | Low                        |  |

| 0  | 1  | 0  | High                       | Low                        | High                       |  |

| 0  | 1  | 1  | High                       | Low                        | Low                        |  |

| 1  | 0  | 0  | Low                        | High                       | High                       |  |

| 1  | 0  | 1  | Low                        | High                       | Low                        |  |

| 1  | 1  | 0  | Low                        | Low                        | High                       |  |

| 1  | 1  | 1  | Low                        | Low                        | Low                        |  |

Note: CF<sub>OUT</sub>, DF<sub>OUT</sub> and PF<sub>OUT</sub> are high when system reset. (Over current detection is disable when DF<sub>OUT</sub> is high.)

#### Table 7 Multiplexer Control

| D2 | D1 | D0 | Output                          |

|----|----|----|---------------------------------|

| 0  | 0  | 0  | Open output (floating) select   |

| 0  | 0  | 1  | Open output (floating) select   |

| 0  | 1  | 0  | Open output (floating) select   |

| 0  | 1  | 1  | Open output (floating) select   |

| 1  | 0  | 0  | Charge current output select    |

| 1  | 0  | 1  | Discharge current output select |

| 1  | 1  | 0  | Battery voltage output select   |

| 1  | 1  | 1  | GND output select               |

Note: Multiplexer output is floating when system reset

#### Table 8 Conditioning Circuit

| D2 | D1 | D0 | Output                                           |

|----|----|----|--------------------------------------------------|

| 0  | 0  | 0  | Open                                             |

| 0  | 0  | 1  | V1 conditioning (short $V_{IN1}$ and $V_{IN2}$ ) |

| 0  | 1  | 0  | V2 conditioning (short $V_{IN2}$ and $V_{IN3}$ ) |

| 0  | 1  | 1  | V3 conditioning (short $V_{IN3}$ and $V_{IN4}$ ) |

| 1  | 0  | 0  | V4 conditioning (short V <sub>IN4</sub> and GND) |

| 1  | 0  | 1  | V1 to V4 conditioning (discharge all cells)      |

| 1  | 1  | 0  | Open                                             |

| 1  | 1  | 1  | Open                                             |

Note: Conditioning circuit is floating when system reset

### Table 9 Regulator, Over Current Detection Control

|    |    |    | Output                          |                                |  |

|----|----|----|---------------------------------|--------------------------------|--|

| D2 | D1 | D0 | Regulator                       | Over Current Detection Circuit |  |

| 0  | 0  | 0  | ON                              | ON                             |  |

| 0  | 0  | 1  | OFF (GND output) * <sup>1</sup> | *1                             |  |

| 0  | 1  | 0  | ON                              | Capacity delay terminal L fix  |  |

| 0  | 1  | 1  | ON                              | Capacity delay terminal H fix  |  |

| 1  | 0  | 0  | Don't care                      | Don't care                     |  |

| 1  | 0  | 1  | Don't care                      | Don't care                     |  |

| 1  | 1  | 0  | Don't care                      | Don't care                     |  |

| 1  | 1  | 1  | Don't care                      | Don't care                     |  |

Note: The regulator output is enable when system reset.

1. All functions of M61040 are stooped. But if the charger is connected then M61040 will not enter power down mode.

RENESAS

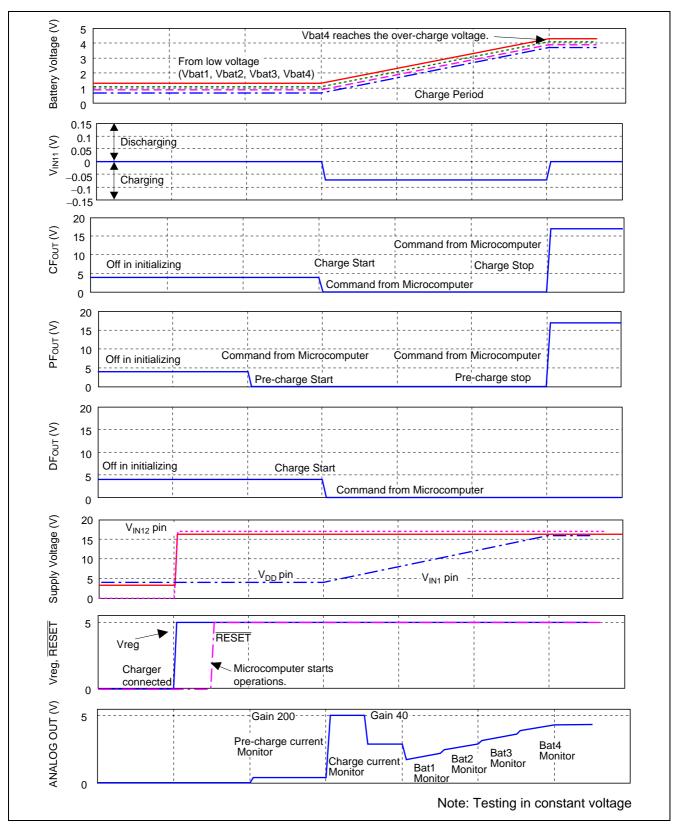

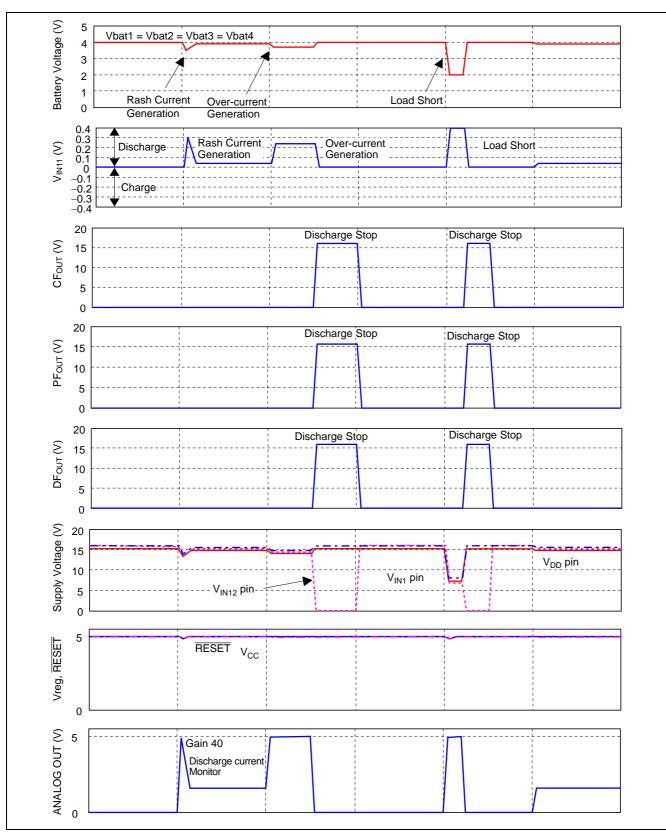

## **Timing Chart**

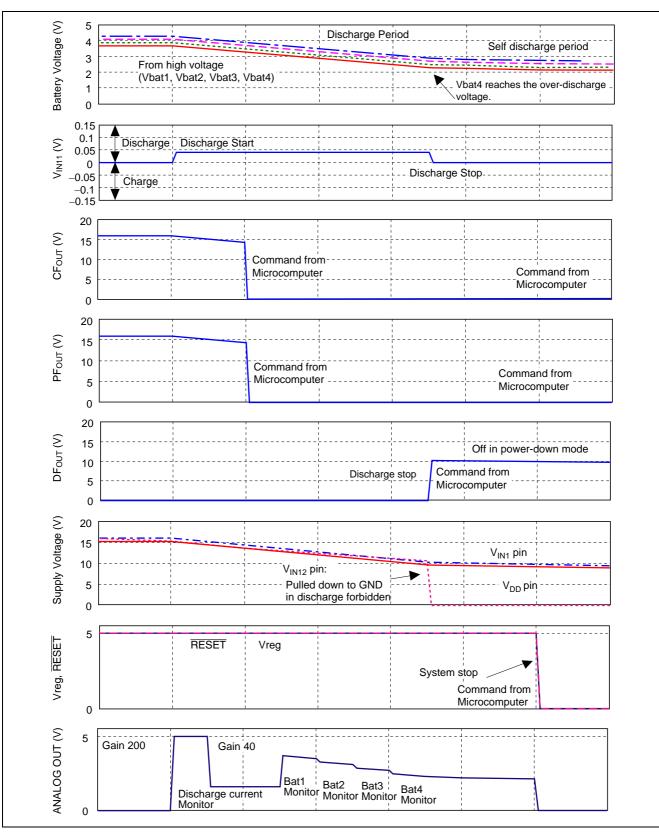

### **Discharge Sequence**

RENESAS

### **Discharge Sequence**

#### **Over Current Detection Sequence**

## **Application Circuit**

### Table 10 Fixed Number

| Symbol            | Components          | Purpose                             | Recommend | Min     | Max     | N.B.                                            |

|-------------------|---------------------|-------------------------------------|-----------|---------|---------|-------------------------------------------------|

| D1                | Diode               | Supply voltage                      | _         | —       | -       | Please take care the maximum power dissipation. |

| D2                | Diode               | Supply voltage                      | -         | _       | _       | Please take care the maximum power dissipation. |

| DFET              | Pch MOSFET          | Discharge control                   | _         | _       | _       |                                                 |

| CFET              | Pch MOSFET          | Charge control                      | _         | _       |         | _                                               |

| PFET              | Nch MOSFET          | Precharge control                   | _         | _       | _       | _                                               |

| RCF1              | Resistor            | Pull down resistor                  | 1 MΩ      | 100 kΩ  | 3 MΩ    | _                                               |

| RCF2              | Resistor            | Current limit                       | 100 kΩ    | _       | 1 MΩ    | _                                               |

| RPF1              | Resistor            | Pull down resistor                  | 1 MΩ      | 100 kΩ  | 3 MΩ    | _                                               |

| RPF2              | Resistor            | Precharge current control           | 1 kΩ      | _       | _       | _                                               |

| RPF3              | Resistor            | Current limit                       | 100 kΩ    | _       | 1 MΩ    | _                                               |

| R <sub>IN1</sub>  | Resistor            | Measure for ESD                     | 10 Ω      | _       | 1 kΩ    | _                                               |

| C <sub>IN1</sub>  | Capacitor           | Measure for ripples of power supply | 0.22 μF   | _       | 1.0 μF  |                                                 |

| R <sub>IN2</sub>  | Resistor            | Measure for ESD                     | 1 kΩ      |         | 10 kΩ   | _                                               |

| $C_{\text{IN2}}$  | Capacitor           | Measure for ripples of power supply | 0.22 μF   | -       | 1.0 μF  |                                                 |

| R <sub>IN3</sub>  | Resistor            | Measure for ESD                     | 1 kΩ      | _       | 10 kΩ   | Please set up same value as<br>RIN2, CIN2       |

| C <sub>IN3</sub>  | Capacitor           | Measure for ripples of power supply | 0.22 μF   | _       | 1.0 μF  |                                                 |

| R <sub>IN4</sub>  | Resistor            | Measure for ESD                     | 1 kΩ      | _       | 10 kΩ   | Please set up same value as                     |

| C <sub>IN4</sub>  | Capacitor           | Measure for ripples of power supply | 0.22 μF   | -       | 1.0 μF  | RIN2, CIN2                                      |

| CICT              | Capacitor           | Set up delay time                   | 0.01 μF   | _       | 0.47 μF | _                                               |

| R <sub>IN12</sub> | Resistor            | Measure for ESD                     | 10 kΩ     | 300 Ω   | 200 kΩ  | _                                               |

| CV <sub>cc</sub>  | Capacitor           | Measure for ripples of power supply | 0.22 μF   | _       | _       | _                                               |

| RSENCE            | Sensing<br>resistor | Charge/discharge current monitor    | 20 mΩ     | _       | _       | -                                               |

| R <sub>IN11</sub> | Resistor            | Measure for ripples of power supply | 100 Ω     | —       | 1 kΩ    | -                                               |

| C <sub>IN11</sub> | Capacitor           | Measure for ripples of power supply | 0.1 μF    | —       | 1.0 μF  |                                                 |

| CREG              | Capacitor           | Eliminate the voltage noise         | 4.7 μF    | 0.47 μF | —       | -                                               |

| CREF              | Capacitor           | Eliminate the voltage noise         | 4.7 μF    | —       | —       | -                                               |

| RRESET            | Resistor            | Set up delay time                   | 47 kΩ     | 10 kΩ   | 3 MΩ    | It is necessary that you adjust                 |

| CRSET             | Capacitor           | Set up delay time                   | 0.1 μF    | —       | —       | a delay time for MCU.                           |

| RCK               | Resistor            | Pull down resistor                  | _         | 100 kΩ  | _       | _                                               |

| RCS               | Resistor            | Pull down resistor                  | _         | 100 kΩ  | —       | _                                               |

| RDI               | Resistor            | Pull down resistor                  | _         | 100 kΩ  | _       | _                                               |

## Package Dimensions

20P2X-A

Note: Please contact Renesas Technology Corp. for further details.

## RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

But not infinited to, product data. diagrams, charts, programs, algorithms, and application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulation.

All information in this document, included in this document for the purpose of military application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulations.

All information included in this document such as product data, diagrams, charts, programs, algorithms, and application carcuit examples, is current as of the date this document, when exporting the products or the technology described herein, you should follow the applicable export control laws and regulations.

Renesas has used reasonable care in compiling the information in this document, but Renesas assumes no liability whatsoever for any damages incurred as a coupling or otherwise relying on the information included in this document. Dut Renesas asproaces for descing about the applicability or otherwise in systems before deciding about the applicability or draws are relying on the information in this document. Dut Renesas asproaces are descing about the applicability of the total system before deciding about the applicability or draws are strained information in this document. Dut Renesas asproaces are not designed many particular or draws and splications, and processes and applications, and processes to the applicability of the systems of the systems or terms provide asproace and accument. To otherwise in systems the failure of mathin dr

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com